芯片资讯

你的位置:SITIME(赛特时脉)预编程振荡器/晶振全系列-亿配芯城 > 芯片资讯 > 汤谷智能发布全栈RISC-V硬件仿真加速系统方案

汤谷智能发布全栈RISC-V硬件仿真加速系统方案

- 发布日期:2024-01-26 06:55 点击次数:209

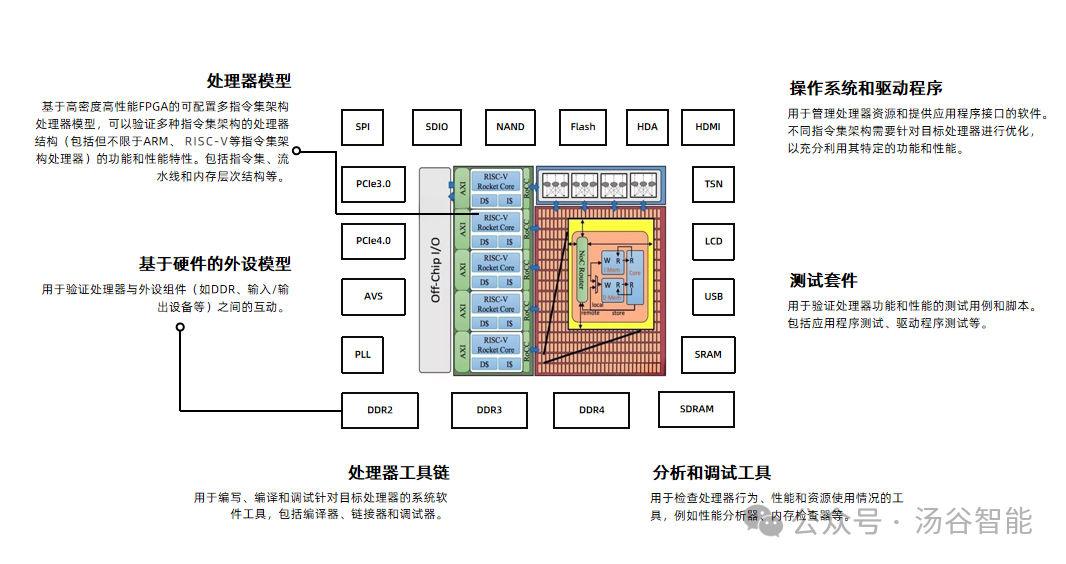

面向高性能计算、IoT、无线接入、音频、多媒体、消费类电子、边缘计算等迅速扩展的RISC-V使用场景,汤谷智能发布了基于自研Logic Giant原型验证硬件平台的全栈RISC-V硬件仿真加速系统方案。

方案可支持阿里玄铁、香山南湖等多款常用RISC-V Core,并同时支持Verilog及Chisel等多种设计语言,配合自研TGOriPartition软件工具,支持多核、大规模分割。支持MCU到AP多个处理器级别,流水线从2级到12级。方案支持基于RISC-V的SoC系统,常用外设齐全,可通过EDA工具选择不同的RISC-V Core和外设,自动生成可直接在原型平台运行的SoC系统,支持适配SoC系统的驱动软件及操作系统运行, 电子元器件采购网 极大提高开发效率。

从客户使用效果来看,方案可同时支持8路以上可编程独立时钟源,每一路都能支特全局时钟同步,传输距离为1.5米时,采用LVDS 传输性能可大于1.6Gbps,延迟小于900ps。采用自研的互联IP总线和电缆,超低延迟可同时运行512个RISC-V Core并保持系统统一同步运行,系统主频可达到8~10MHZ以上。

为了支持多个用户的同时使用的场景,方案中单个机箱可支持几十个虚拟用户和真实5用户同时使用,特别是真实5用户可动态独立使用分配到的FPGA逻辑资源,不与其他用户从逻辑、时钟、复位和外设等各种资源产生冲突。

审核编辑:汤梓红

相关资讯

- 被动元件大厂国巨集团旗下基美发布钽电容涨价20%-30%!2025-11-04

- 芯片供应链在人工智能和电子制造中的重要角色2025-04-28

- 禾赛科技激光雷达交付创新高,512线超高清超远距新品发布2024-01-13

- 沃尔玛推出生成式人工智能工具2024-01-11

- 工信部:50余项云计算标准化体系建设指南发布,推进云计算行业发展2024-01-11

- 智能遥控器生产及解决方案提供商辰奕智能成功上市2024-01-09